### Scalable 5 A full-bridge driver for brushed DC motors

#### **Features**

- Operating voltage up to 58V

- Maximum output current up to 5 Arms

- Seven driving methods with dual half-bridge, single full-bridge and half-bridge parallel mode

- $R_{DS(ON)}$  HS + LS = 0.33  $\Omega$  typ.

- Adjustable power MOS slew rate

- Integrated amplifiers with two different embedded current control techniques

- Adjustable OFF-time with slow or mixed decay

- Low consumption standby

- **Protections**

- **UVLO**

- Overcurrent protection

- Thermal shutdown

# **Application**

- Stage lighting

- Factory automation

- ATM and money handling machines

- Textile machines

- Home appliances

- Robotics

- Antenna control

- Vending machines

#### **Product status link**

STSPIN958

#### **Product label**

#### **Description**

The STSPIN958 is a 5A full bridge driver for brushed DC motors.

The power stage is designed with high dynamic performance, allowing to achieve high frequency PWM control with precise duty-cycle.

The device offers a current limiter with adjustable threshold and off-time with slow or mixed decay selection. Two amplifiers with fixed amplification factor are available for current sensing (using an external shunt resistor).

The adjustable slew-rate guarantees the best trade-off between performances and

Versatile power stage offers seven different ways of operation for a high level of flexibility.

The device offers a complete set of protection features including overcurrent, overtemperature and low bus voltage detection.

# 1 Block diagram

VS VBOOT GND PUMP V2 V1 -□-□ VDD REF CHARGE UVLO CP2 [ PUMP CP1[ OVT nSTBY [ vs EN/nFAULT OUT1 ₽ LSS1 MODE1 [ CONTROL LOGIC MODE2 | □ OUT2 MODE3 [ PWM1 ☐ OFFSET PWM2/PH [ Ϋ́ Monostable (fixed t<sub>OFF</sub>) TOFF Digital buffer PWM trimming) SR

Figure 1. Block diagram

DS14341 - Rev 3 page 2/35

# 2 Electrical data

### 2.1 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in Table 1 may cause permanent damage to the device. Exposure to maximum rating conditions for extended periods may affect device reliability.

Table 1. Absolute maximum ratings

| Symbol                                | Parameter                               | Test condition                                             | Value                    | Unit             |

|---------------------------------------|-----------------------------------------|------------------------------------------------------------|--------------------------|------------------|

| $V_{DD}$                              | Control logic supply voltage            |                                                            | -0.3 to 4                | V                |

| Vs                                    | Power stage supply voltage              |                                                            | -0.3 to 62               | V                |

| dV <sub>S</sub> /dt                   | Supply voltage gradient                 |                                                            | 0.5                      | V/µs             |

| V <sub>SPUMP</sub>                    | Charge pump input voltage               |                                                            | V <sub>S</sub> +/- 0.1 V | V                |

| V <sub>BOOT</sub>                     | Bootstrap voltage                       |                                                            | -0.3 to 62               | V                |

| 1/                                    | 0.1.1.11                                | V <sub>S</sub> < 61.4 V                                    | V <sub>S</sub> + 0.6     | .,               |

| V <sub>OUT</sub>                      | Output voltage                          | V <sub>S</sub> ≥ 61.4 V                                    | 62                       | V                |

| I <sub>OUT</sub>                      | DC output current                       | Each output                                                | Up to 5                  | A <sub>rms</sub> |

| I <sub>OUT,peak</sub>                 | Peak output current                     |                                                            | Limited by OC protection | Α                |

| V <sub>LSS</sub>                      | Low-side source voltage (LSSxx pins)    |                                                            | -0.6 to +2               | V                |

| V <sub>REFA</sub> , V <sub>REFB</sub> | Voltage range at pins REFA and REFB     | V <sub>DD</sub> = 4 V                                      | -0.3 to V <sub>DD</sub>  | V                |

| V <sub>SR</sub>                       | Voltage range at pin SR                 | V <sub>DD</sub> = 4 V                                      | -0.3 to V <sub>DD</sub>  | V                |

| V <sub>TOFFx</sub>                    | Voltage range at pins T <sub>OFFx</sub> | V <sub>DD</sub> = 4 V                                      | -0.3 to V <sub>DD</sub>  | V                |

| V <sub>IN</sub>                       | Logic input voltage                     | All digital inputs excluded MODE1, MODE2, MODE3 and OFFSET | -0.3 to 5.5              | V                |

|                                       |                                         | MODE1, MODE2,<br>MODE3 and OFFSET                          | -0.3 to V <sub>DD</sub>  | V                |

| I <sub>OD</sub>                       | Open drain outputs sink current         | nFAULT                                                     | Up to 8                  | mA               |

| T <sub>stg</sub>                      | Storage temperature                     |                                                            | -55 to 150               | °C               |

| Тј                                    | Junction temperature                    |                                                            | -40 to 150               | °C               |

# 2.2 Recommended operating conditions

Table 2. Recommended operating conditions

| Symbol                        | Parameter                    | Test condition | Min.               | Тур. | Max.              | Unit |

|-------------------------------|------------------------------|----------------|--------------------|------|-------------------|------|

| V <sub>DD</sub>               | Control logic supply voltage |                | 2.8 <sup>(1)</sup> | 3.3  | 3.6               | V    |

| V <sub>S</sub> <sup>(2)</sup> | Power stage supply voltage   |                | 5.05               |      | 58 <sup>(3)</sup> | V    |

| V <sub>SPUMP</sub>            | Charge pump input voltage    |                |                    | Vs   |                   | V    |

DS14341 - Rev 3 page 3/35

| Symbol                                | Parameter                              | Test condition                                                  | Min. | Тур.        | Max.               | Unit |

|---------------------------------------|----------------------------------------|-----------------------------------------------------------------|------|-------------|--------------------|------|

| V <sub>BO</sub>                       | Bootstrap overdrive voltage            | V <sub>BOOT</sub> – V <sub>S</sub>                              |      | 3           |                    | V    |

| V <sub>REFA</sub>                     | Voltage range at pin REF               |                                                                 | 0.1  |             | $V_{DD}$           | V    |

| V <sub>LSS1</sub> , V <sub>LSS2</sub> | Low-side source voltage                |                                                                 | -0.6 |             | +1                 | V    |

| V <sub>OUT</sub>                      | Output voltage                         |                                                                 | -0.6 |             | Vs                 | V    |

|                                       |                                        | Excluded                                                        |      |             |                    |      |

|                                       |                                        | MODE1,                                                          |      |             |                    |      |

|                                       |                                        | MODE2,                                                          | 0    |             | 5                  | V    |

|                                       |                                        | MODE3,                                                          | U    |             | 5                  | V    |

|                                       |                                        | OFFSETA and                                                     |      |             |                    |      |

| V <sub>IN</sub> <sup>(4)</sup>        | Logic input voltage                    | OFFSETB                                                         |      |             |                    |      |

|                                       |                                        | MODE1,                                                          |      |             |                    |      |

|                                       |                                        | MODE2,                                                          |      |             |                    |      |

|                                       |                                        | MODE3,                                                          | 0    |             | VDD                | V    |

|                                       |                                        | OFFSETA and                                                     |      |             |                    |      |

|                                       |                                        | OFFSETB                                                         |      |             |                    |      |

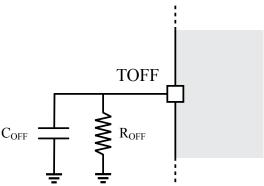

| R <sub>TOFF</sub>                     | Current limiter time setting resistor  | Enabled fixed OFF-time current limiter mode (see Section 5.6.1) | 10   |             | 120                | kΩ   |

| C <sub>TOFF</sub>                     | Current limiter time setting capacitor | Enabled fixed OFF-time current limiter mode (see Section 5.6.1) | 0.1  |             | 5.6                | nF   |

| R <sub>SR</sub>                       | Slew rate selection resistor           |                                                                 |      | See Table 7 | ,                  |      |

| t <sub>pulse</sub>                    | Minimum PWM pulse width                |                                                                 | 280  |             |                    | ns   |

|                                       | Charge pump capacitor                  | C <sub>CP</sub> = 100 nF                                        |      |             |                    |      |

| t <sub>BOOT</sub>                     | charging time                          | C <sub>BOOT</sub> = 1 μF                                        |      | 170         |                    | μs   |

| f <sub>PWM</sub>                      | Switching frequency                    |                                                                 | 0    |             | 500 <sup>(5)</sup> | kHz  |

| C <sub>BOOT</sub>                     | Bootstrap capacitor                    |                                                                 |      | 1           |                    | μF   |

| C <sub>CP</sub>                       | Charge pump capacitor                  |                                                                 |      | 100         |                    | nF   |

| T <sub>amb</sub>                      | Ambient temperature                    |                                                                 | -40  |             | 85 <sup>(2)</sup>  | °C   |

- 1. Actual operative range can be limited by UVLO protections

- 2. Actual operative range according to heat dissipation performance of the application

- 3. In specific conditions (Tj  $\geq$  75 °C and RH  $\geq$  60%), the maximum  $V_S$  voltage is sustainable for a limited period

- 4. All digital inputs (excluding MODE1, MODE2, MODE3, and OFFSET) are 5 V tolerant

- 5. Actual operative range can be limited by the selected slew rate

# 2.3 ESD protection ratings

Table 3. ESD protection ratings

| Symbol | Parameter           | Condition                                          | Class | Value | Unit |

|--------|---------------------|----------------------------------------------------|-------|-------|------|

| HBM    | Human body model    | Conforming to ANSI/ESDA/JEDEC JS-001-2014          | H2    | 2     | kV   |

| CDM    | Charge device model | All pins Conforming to ANSI/ESDA/JEDEC JS-002-2014 | C2a   | 500   | V    |

|        |                     | Corner pins only                                   | C2    | 750   | V    |

DS14341 - Rev 3 page 4/35

| Symbol | Parameter           | Condition                                 | Class | Value | Unit |

|--------|---------------------|-------------------------------------------|-------|-------|------|

| CDM    | Charge device model | Conforming to ANSI/ESDA/JEDEC JS-002-2014 |       |       |      |

### 2.4 Thermal data

Table 4. Thermal data

| Symbol               | Parameter                                         | Condition                                                           | Value | Unit |

|----------------------|---------------------------------------------------|---------------------------------------------------------------------|-------|------|

| R <sub>thJA</sub>    | Junction to ambient thermal resistance            | Natural convection, according to JESD51-2a <sup>(1)</sup>           | 35.8  | °C/W |

| R <sub>thJCtop</sub> | Junction to case thermal resistance (top side)    | Cold plate on package top, according to JESD51-12.01 <sup>(1)</sup> | 22.8  | °C/W |

| R <sub>thJCbot</sub> | Junction to case thermal resistance (bottom side) | Cold plate on exposed pad, according to JESD51-12.01 <sup>(1)</sup> | 4     | °C/W |

| R <sub>thJB</sub>    | Junction to board thermal resistance              | According to JESD51-8 <sup>(1)</sup>                                | 17.4  | °C/W |

| $\Psi_{JT}$          | Junction to top characterization                  | According to JESD51-12.01 <sup>(1)</sup>                            | 0.2   | °C/W |

| $\Psi_{JB}$          | Junction to board characterization                | According to JESD51-12.01 <sup>(1)</sup>                            | 17    | °C/W |

<sup>1.</sup> Simulated as per standard JEDEC (JESD51-7) in natural convection

DS14341 - Rev 3 page 5/35

# 3 Electrical characteristics

Testing conditions:  $V_S$  = 58 V,  $V_{BOOT}$  = 61 V,  $V_{DD}$  = 3.3 V, unless otherwise specified.

Typical values are tested at  $T_j$  = 25 °C, minimum and maximum values are guaranteed by thermal characterization in the temperature range of -40 to 125 °C, unless otherwise specified.

**Table 5. Electrical characteristics**

| Symbol                                                                                                          | Parameter                                                           | Test condition                                                               | Min. | Тур. | Max. | Unit                                  |

|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------|------|------|------|---------------------------------------|

| Supply                                                                                                          |                                                                     | '                                                                            |      |      |      |                                       |

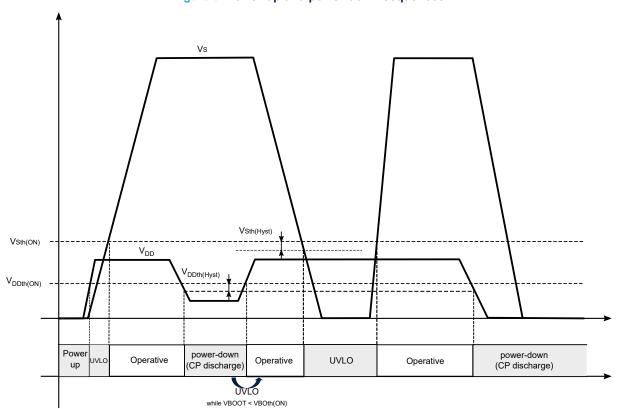

| V <sub>DDth(ON)</sub>                                                                                           | V <sub>DD</sub> power-on reset                                      | V <sub>DD</sub> rising                                                       |      |      | 2.7  | V                                     |

| V <sub>DDth(Hyst)</sub>                                                                                         | V <sub>DD</sub> power-on reset hysteresis                           | V <sub>DD</sub> falling<br>(V <sub>DDth(ON)</sub> - V <sub>DDth(OFF)</sub> ) | 100  |      | 300  | mV                                    |

| V <sub>Sth(ON)</sub>                                                                                            | V <sub>S</sub> turn-on threshold                                    | V <sub>S</sub> rising                                                        |      |      | 5.05 | V                                     |

| V <sub>Sth(Hyst)</sub>                                                                                          | V <sub>S</sub> turn-on threshold hysteresis                         | V <sub>S</sub> falling (V <sub>Sth(ON)</sub> – V <sub>Sth(OFF)</sub> )       | 100  |      | 300  | mV                                    |

| V <sub>BO</sub>                                                                                                 | Bootstrap overdrive voltage  V <sub>BOOT</sub> - V <sub>SPUMP</sub> |                                                                              |      | 3    |      | V                                     |

| V <sub>BOth(ON)</sub>                                                                                           | V <sub>BO</sub> turn-on threshold                                   | V <sub>BO</sub> rising                                                       |      |      | 2    | V                                     |

| I <sub>DD,STBY</sub>                                                                                            | V <sub>DD</sub> consumption in standby                              | Standby                                                                      |      |      | 3    | μA                                    |

| I <sub>S,STBY</sub>                                                                                             | V <sub>S</sub> consumption in standby                               | Standby                                                                      |      |      | 1    | μΑ                                    |

| t <sub>STBY</sub>                                                                                               | Standby time                                                        |                                                                              |      |      | 600  | μs                                    |

| t <sub>WAKE</sub>                                                                                               | Wake-up time                                                        |                                                                              |      |      | 10   | μs                                    |

| Power stag                                                                                                      | e                                                                   | '                                                                            |      |      |      |                                       |

| R <sub>DS(ON),LS</sub>                                                                                          | Low-side turn-on resistance                                         | T <sub>j</sub> = 25 °C                                                       |      | 165  |      | mΩ                                    |

| R <sub>DS(ON),HS</sub>                                                                                          | High-side turn-on resistance                                        | T <sub>j</sub> = 25 °C                                                       |      | 165  |      | mΩ                                    |

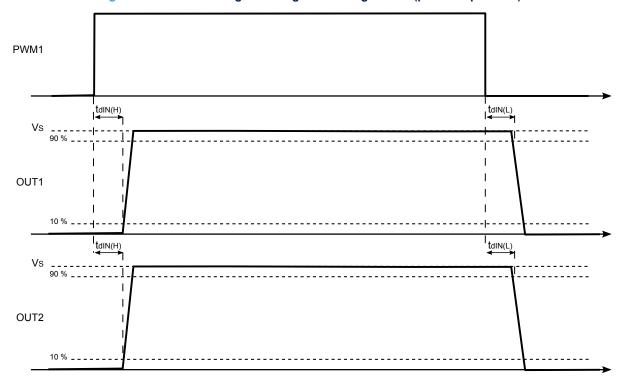

| t <sub>dIN(H)</sub>                                                                                             | Input high to high-side turn-on propagation delay                   | Maximum slew rate                                                            |      | 300  |      | ns                                    |

| t <sub>dIN(L)</sub>                                                                                             | Input low to low-side turn-on propagation delay                     | Maximum slew rate                                                            |      | 300  |      | ns                                    |

| MT                                                                                                              | Delay matching, HS and LS turn-on/off                               | Maximum slew rate $MT =  t_{dH} - t_{dL} $                                   |      |      | 50   | ns                                    |

|                                                                                                                 |                                                                     | R <sub>SR</sub> = 1 kΩ                                                       |      | 2    |      |                                       |

| CD.                                                                                                             | Pision also note                                                    | $R_{SR}$ = 2.2 k $\Omega$                                                    |      | 1.2  |      | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| SK <sub>rise</sub>                                                                                              | Rising slew rate                                                    | $R_{SR}$ = 5.6 k $\Omega$                                                    |      | 0.6  |      | V/ns                                  |

|                                                                                                                 |                                                                     | $R_{SR}$ = 10 k $\Omega$                                                     |      | 0.3  |      |                                       |

|                                                                                                                 |                                                                     | R <sub>SR</sub> = 1 kΩ                                                       |      | 2    |      |                                       |

| SReal                                                                                                           | Falling slew rate                                                   | $R_{SR}$ = 2.2 k $\Omega$                                                    |      | 1.2  |      | V/ns                                  |

| Is,stby  tstby  twake  Power stage  RDS(ON),LS  RDS(ON),HS  tdIN(H)  tdIN(L)  MT  SRrise  SRfall  Logic input a | r anning siew rate                                                  | $R_{SR}$ = 5.6 k $\Omega$                                                    | 0.6  |      |      | VIIIS                                 |

|                                                                                                                 |                                                                     | $R_{SR}$ = 10 k $\Omega$                                                     |      | 0.3  |      |                                       |

| Logic input                                                                                                     | and outputs                                                         |                                                                              | ı    |      |      |                                       |

| V <sub>IL</sub>                                                                                                 | Low logic input voltage                                             |                                                                              |      |      | 0.8  | V                                     |

| V <sub>IH</sub>                                                                                                 | High logic input voltage                                            |                                                                              | 2    |      |      | V                                     |

| $V_{IL(EN)}$                                                                                                    | Enable low logic input voltage                                      |                                                                              |      |      | 0.4  | V                                     |

DS14341 - Rev 3 page 6/35

| Symbol                  | Parameter                                        | Test condition              | Min. | Тур. | Max. | Unit |

|-------------------------|--------------------------------------------------|-----------------------------|------|------|------|------|

| V <sub>IH(EN)</sub>     | Enable high logic input voltage                  |                             | 2.55 |      |      | V    |

| V <sub>OL(nFAULT)</sub> | Low logic level output voltage (EN/nFAULTx)      | I <sub>SINK</sub> = 4 mA    |      |      | 0.4  | V    |

| V <sub>FAULT</sub>      | FAULT open drain release threshold               |                             | 0.4  |      | 0.6  | V    |

| I <sub>PD</sub>         | EN/nFAULTA and EN/nFAULTB pull-down current      |                             |      | 5    |      | μA   |

| R <sub>PDin</sub>       | Input pull-down resistor                         |                             |      | 500  |      | kΩ   |

| R <sub>PUin</sub>       | Input pull-up resistor (MODE1, MODE2, and MODE3) |                             |      | 500  |      | kΩ   |

| Current limi            | ter                                              |                             |      |      |      |      |

|                         |                                                  | R <sub>OFF</sub> = 10 kΩ    |      |      |      |      |

|                         | Current limiter off-time                         | C <sub>OFF</sub> = 0.1 nF   |      | 1    |      | μs   |

| t <sub>OFF</sub>        | See Figure 9                                     | R <sub>OFF</sub> = 120 kΩ   |      | 500  |      |      |

|                         |                                                  | C <sub>OFF</sub> = 5.6 nF   |      | 500  |      | μs   |

| Integrated a            | mplifier                                         |                             |      |      |      |      |

| A <sub>CL</sub>         | Gain                                             | Full temp range             | 9.5  | 10   | 10.5 | V/V  |

|                         |                                                  | V <sub>in</sub> 150 mV step |      |      |      |      |

| t <sub>settling</sub>   | Output voltage settling time                     | C <sub>L</sub> = 100 pF     |      |      | 200  | ns   |

| Protections             |                                                  |                             |      |      |      |      |

| loc                     | Overcurrent threshold                            |                             | 7    | 10   | 14   | Α    |

| T <sub>SD</sub>         | Thermal shutdown threshold                       |                             | 150  |      |      | °C   |

| T <sub>SD(Hyst)</sub>   | Thermal shutdown hysteresis                      |                             |      | 30   |      | °C   |

DS14341 - Rev 3 page 7/35

# 4 Pin description

Figure 2. Pin connection 24 LSS2 LSS1 23 LSS1 LSS2 2 **GNDPUMP GND VSPUMP** SR CP1 (20 MODE1 CP2 19 **EPAD** MODE2 **VBOOT** 18 MODE3 V1 (17 8 V2 10 11 12 13 14 15 16 PWM2 VDD nSTBY REF

Table 6. Pad list

| N. | Name    | Туре          | Function                                                                            |

|----|---------|---------------|-------------------------------------------------------------------------------------|

| 1  | LSS1    | Power         | Low-side source half-bridge 1                                                       |

| 2  | LSS1    | Power         | Low-side source half-bridge 1                                                       |

| 3  | GNDPUMP | Ground        | Ground charge pump                                                                  |

|    |         |               | Supply charge pump circuitry (internally connected to VS).                          |

| 4  | VSPUMP  | Supply        | In application must be connected to the CBOOT. It can be shorted to VS supply       |

| 5  | CP1     | Analog output | Charge pump oscillator output1                                                      |

| 6  | CP2     | Analog output | Charge pump oscillator output2                                                      |

| 7  | VBOOT   | Supply        | Bootstrap voltage needed to drive the high-side MOSFETs                             |

| 8  | V1      | Analog output | Amplified sense signal, half bridge 1                                               |

| 9  | OFFSET  | Digital input | Voltage level shift                                                                 |

| 10 | nSTBY   | Digital input | Active low standby input. When forced low the device enters in low consumption mode |

| 11 | PWM1    | Digital input | Half-bridge 1 PWM input                                                             |

DS14341 - Rev 3 page 8/35

| N. | Name                | Туре                          | Function                                                                                                                                                                       |

|----|---------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12 | PWM2/PH             | Digital input                 | Half-bridge 2 PWM input/Phase input                                                                                                                                            |

| 13 | VDD                 | Supply                        | Supply digital logic                                                                                                                                                           |

| 14 | EN/nFAULT           | Logic input/open drain output | Logic input with open drain output.  Full bridge enable (when low, the power stage is turned off); it is forced low by the integrated open-drain MOSFET when a failure occurs. |

| 15 | REF                 | Analog input                  | Reference voltage for PWM current limiter circuitry                                                                                                                            |

| 16 | TOFF <sup>(B)</sup> | Analog input Digital output   | PWM current limiter off-time adjustment in fixed off-time mode  Decay output signal in PWM trimming mode                                                                       |

| 17 | V2                  | Analog output                 | Amplified sense signal, half bridge 2                                                                                                                                          |

| 18 | MODE3               | Digital input                 | Mode selector pin 3                                                                                                                                                            |

| 19 | MODE2               | Digital input                 | Mode selector pin 2                                                                                                                                                            |

| 20 | MODE1               | Digital input                 | Mode selector pin 1                                                                                                                                                            |

| 21 | SR                  | Analog input                  | Slew rate value selection                                                                                                                                                      |

| 22 | GND                 | Ground                        | Device ground                                                                                                                                                                  |

| 23 | LSS2                | Power                         | Low-side source half-bridge 2                                                                                                                                                  |

| 24 | LSS2                | Power                         | Low-side source half-bridge 2                                                                                                                                                  |

| 25 | OUT2                | Power                         | Power output half-bridge 2                                                                                                                                                     |

| 26 | OUT2                | Power                         | Power output half-bridge 2                                                                                                                                                     |

| 27 | VS                  | Supply                        | Supply output power stages                                                                                                                                                     |

| 28 | VS                  | Supply                        | Supply output power stages                                                                                                                                                     |

| 29 | VS                  | Supply                        | Supply output power stages                                                                                                                                                     |

| 30 | VS                  | Supply                        | Supply output power stages                                                                                                                                                     |

| 31 | OUT1                | Power                         | Power output half-bridge 1                                                                                                                                                     |

| 32 | OUT1                | Power                         | Power output half-bridge 1                                                                                                                                                     |

DS14341 - Rev 3 page 9/35

### 5 Description

The STSPIN958 is a protected full bridge with low R<sub>DS(ON)</sub> and high current capability.

The power stages are designed with high dynamic performance allowing to achieve high frequency PWM control with precise duty-cycle.

It integrates a full set of protections, PWM current limiter circuitry and amplifiers for the current sensing through an external shunt resistor.

#### 5.1 Power supply

The device has three supply pins:

- VDD is the control logic supply voltage

- VS is the supply voltage for all the power stage

- VBOOT is the supply voltage for high-side gate drivers

During the power-up, the device is in Under Voltage Lock Out condition (UVLO) until the VS supply voltage rises above the  $V_{Sth(ON)}$  threshold and the VBOOT supply voltage rises above the  $V_{BOth(ON)}$  threshold.

If during the operation the  $V_S$  supply falls below  $V_{Sth(ON)} - V_{Sth(Hyst)}$ , the device returns in UVLO status until the turn-on threshold is exceeded again by Vs.

If during the operation the  $V_{DD}$  supply falls below  $V_{DDth(ON)} - V_{DDth(Hyst)}$ , the device is powered down, power stages are disabled, and all the circuitry (charge pump included) is switched off. When VDD supply rises above  $V_{DDth(ON)}$  the device is in UVLO condition and the charge pump is switched on; the device returns operative as soon as VBOOT rises above the  $V_{BOth(ON)}$  threshold.

If during the operation the  $V_{BOOT}$  supply falls below  $V_{BOth(ON)} - V_{BOth(Hyst)}$ , the device returns in UVLO status until the turn-on threshold is exceeded again.

In UVLO condition, all the MOSFETs are off and the nFAULT is low.

Figure 3. Power-up and power-down sequences

DS14341 - Rev 3 page 10/35

#### 5.2 Power stages and charge pump circuitry

The STSPIN958 integrates power NMOS half-bridges. The input PWM signal drives a corresponding half-bridge according to the driving mode selected (see Section 5.4: Driving logic). In order to achieve a precise duty-cycle and low jitter between different half-bridge activation, the propagation delay of PWM signals is optimized. Cross conduction is prevented thanks to a deadtime between high-side and low-side MOSFET status change.

A blanking circuitry filters the internally generated noise at each commutation of the power stages.

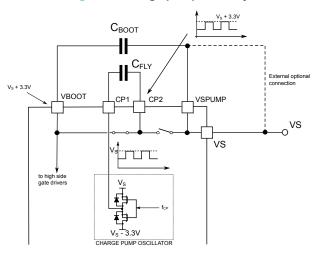

Each gate driving circuit for the high-side MOSFETs is supplied through a charge pump circuitry. The voltage VBOOT is obtained through an internal oscillator with integrated switches and external capacitors implementing a charge pump circuit as shown in Figure 4.

The slew rate of the power bridges output is set according to the value of the resistor connected to the SR pin as reported in Table 7.

| R <sub>SR</sub> (± 5%) | Output slew rate (typ) [V/ns] |

|------------------------|-------------------------------|

| 1 kΩ                   | 2                             |

| 2.2 kΩ                 | 1.2                           |

| 5.6 kΩ                 | 0.6                           |

| 10 kΩ                  | 0.3                           |

Table 7. Slew rate selection

Figure 4. Charge pump circuitry

#### 5.3 Integrated operational amplifiers

The device integrates two operational amplifiers with fixed A<sub>Cl</sub> amplification factor.

Each amplifier is internally connected to the source of a low-side MOSFET (LSS1 and LSS2).

The output is made externally available through a dedicated pin (V1 and V2).

One pin is also available (OFFSET) to allow a voltage level shift. When forced high, the amplifier output is shifted by VDD/2.

#### 5.4 Driving logic

The device supports seven different driving modes according to the status of three input pins as listed in Table 8:

- 1. Dual half-bridge fixed OFF-time

- 2. Single full-bridge fixed OFF-time

- 3. Single half-bridge (parallel mode) fixed OFF-time

- 4. Single full-bridge (mixed decay) fixed OFF-time

- 5. Dual half-bridge PWM trimming

- 6. Single full-bridge PWM trimming

DS14341 - Rev 3 page 11/35

#### 7. Single half-bridge (parallel mode) - PWM trimming

Table 8. Driving mode selection

| MODE1 | MODE2 | MODE3 | Mode                               | Current limiter mode            |

|-------|-------|-------|------------------------------------|---------------------------------|

| LOW   | LOW   | LOW   | Dual half-bridge                   | Fixed OFF-time                  |

| LOW   | HIGH  | LOW   | Single full-bridge                 | Fixed OFF-time                  |

| HIGH  | LOW   | LOW   | Single half-bridge (parallel mode) | Fixed OFF-time                  |

| HIGH  | HIGH  | LOW   | Single full-bridge (mixed decay)   | Fixed OFF-time with mixed decay |

| LOW   | LOW   | HIGH  | Dual half-bridge                   | PWM trimming                    |

| LOW   | HIGH  | HIGH  | Single full- bridge                | PWM trimming                    |

| HIGH  | LOW   | HIGH  | Single half-bridge (parallel mode) | PWM trimming                    |

| HIGH  | HIGH  | HIGH  | Reserved                           | Reserved                        |

#### Important:

It is not allowed to switch from one driving mode to another one during operation. In application, the MODE1, MODE2, and MODE3 inputs should be shorted to ground, left floating, or shorted to VDD.

MODE1, MODE2 and MODE3 inputs integrate an internal pull-up resistor.

EN/nFAULT input has an internal pull-down current.

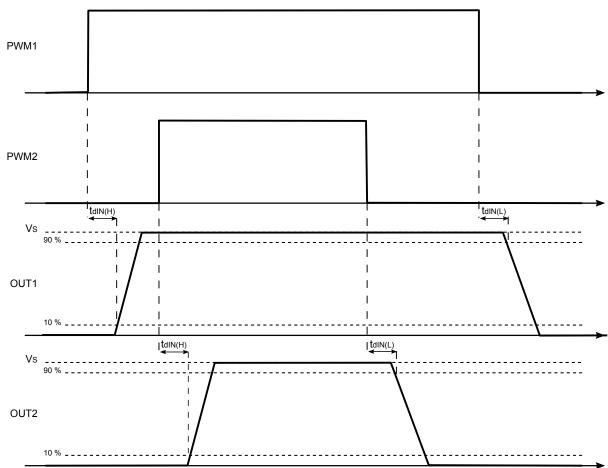

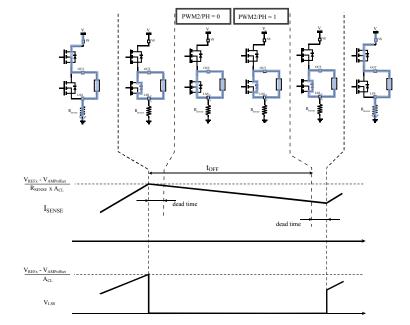

#### 5.4.1 Dual half-bridge mode

In dual half-bridge mode:

- Each PWM input drives the corresponding half-bridge

- Provided that TOFF is not short-circuited to ground, current limiter connected to V1 and REF operates for both the half bridges. When triggered, the low-side MOS is turned on and a slow decay is performed (see Section 5.6.1.1)

- If a fault condition occurs on half-bridge 1 or 2, EN/nFAULT pin is forced low and both the half-bridges are disabled

Table 9. Truth table - dual half-bridge mode

| EN | PWM1             | PWM2/PH          | OUT1       | OUT2       |

|----|------------------|------------------|------------|------------|

| 0  | X <sup>(1)</sup> | X <sup>(1)</sup> | High-Z (2) | High-Z (2) |

| 1  | 1                | 1                | HS on      | HS on      |

| 1  | 0                | 1                | LS on      | HS on      |

| 1  | 1                | 0                | HS on      | LS on      |

| 1  | 0                | 0                | LS on      | LS on      |

- 1. X: don't care

- 2. High-Z: high impedance

DS14341 - Rev 3 page 12/35

Figure 5. Driver time diagram - dual half-bridge mode

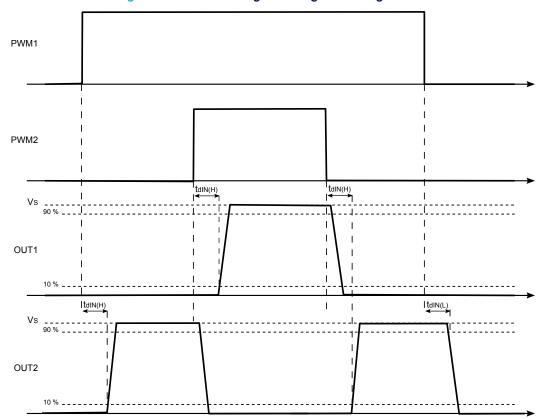

#### 5.4.2 Single full-bridge mode

In single full-bridge mode:

- The outputs of the full-bridge are controlled by the PWM1 and PWM2/PH inputs as reported in Table 10

- When the current limiter is triggered, the low-side MOS is turned on and a slow decay is performed (see Section 5.6.1.1)

- If a fault condition occurs, EN/nFAULT pin is forced low and both the half-bridges (1 and 2) are disabled

ΕN PWM1 PWM2/PH OUT1 OUT2 High-Z<sup>(2)</sup> 0  $X^{(1)}$  $X^{(1)}$ High-Z<sup>(2)</sup> Χ 1 0 LS on LS on 1 1 1 HS on LS on 0 LS on 1 1 HS on

Table 10. Truth table - single full-bridge mode

2. High-Z: high impedance.

DS14341 - Rev 3 page 13/35

<sup>1.</sup> X: don't care.

Figure 6. Driver time diagram - single full-bridge mode

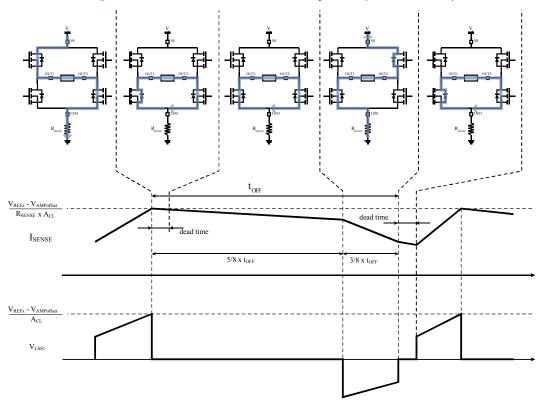

#### 5.4.3 Single half-bridge mode - parallel operation

In this mode, the two half-bridges are driven in parallel to obtain a single high-current and low-resistance path:

- PWM1 and PWM2/PH drive the half-bridges as reported in Table 11.

- When current limiter is triggered, a slow decay is performed and the decay mode is selected through PWM2/PH input (see Section 5.6.1.2 and Section 5.6.2.2):

- if PWM2/PH is low, the low-side MOS is turned on

- if PWM2/PH is high, the output is in high-Z

- If a fault condition occurs, EN/nFAULT pin is forced low and both the half-bridges (1 and 2) are disabled This operation mode requires short-circuiting the following pins:

- OUT1 and OUT2

- LSS1 and LSS2

Table 11. Truth table – single half-bridge mode (parallel operation)

| EN | PWM1             | PWM2/PH                                 | OUT1/2                |

|----|------------------|-----------------------------------------|-----------------------|

| 0  | X <sup>(1)</sup> | X <sup>(1)</sup>                        | High-Z <sup>(2)</sup> |

| 1  | 0                | See Section 5.6.1.2 and Section 5.6.2.2 | LS on                 |

| 1  | 1                | See Section 5.6.1.2 and Section 5.6.2.2 | HS on                 |

- 1. X: don't care.

- 2. High Z: high impedance.

DS14341 - Rev 3 page 14/35

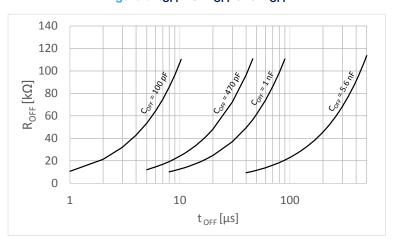

Figure 7. Driver time diagram - single half-bridge mode (parallel operation)

#### 5.4.4 Single full-bridge mode – mixed decay operation

This mode is available only with the current limiter set in fixed OFF-time. The device is driven similarly to "Single full-bridge mode" (see Section 5.4.2); however, when current limiter is triggered, a mixed decay is performed as described in Section 5.6.1.3.

#### 5.5 Standby

The device provides a low consumption mode. In this condition, the charge pump circuitry is turned off.

The device enters the standby mode by forcing low the nSTBY input for at least  $t_{STBY}$ . As soon as the input is high, the device returns operative after  $t_{WAKE}$  +  $t_{BOOT}$ .

In low consumption mode, the EN/nFAULT pin should not be left floating at any times.

During the wake-up, the device is in Under Voltage Lock Out condition (UVLO) until the VBOOT supply voltage rises above the  $V_{BOth(ON)}$  threshold. After  $t_{BOOT}$ , the charge-pump circuitry charges the bootstrap capacitor and the device becomes operative.

#### 5.6 PWM current control

The device integrates a current limiter internally connected to V1 and REF pins.

The input voltage of the amplifier ( $V_{LSS1}$ ) is amplified by  $A_{CL}$  and output at V1. This voltage is compared with the respective reference voltage ( $V_{REF}$ ). When  $V_{V1} > V_{REF}$  the comparator triggers and the device operates according to the selected decay strategy. The reference voltage value,  $V_{REF}$ , must be selected according to the load current target value (peak value), the gain of the embedded amplifier ( $A_{CL}$ ) and the sense resistors value.

#### **Equation 1**

$$V_{REFx} = R_{SENSE} \times A_{CL} \times I_{peak} + V_{AMPoffset}$$

(1)

where  $V_{AMPoffset}$  is equal to 0 (OFFSETx is low) or  $V_{DD}/2$  (OFFSETx is high).

Two current limiter modes are available based on the connection of the pin MODE3 (see Table 8):

- 1. Fixed OFF-time (MODE3 = LOW)

- 2. PWM trimming (MODE3 = HIGH)

DS14341 - Rev 3 page 15/35

#### 5.6.1 Fixed OFF-time mode

When  $V_{1x}$  exceeds  $V_{REFx}$  the control circuitry sets the device in limiting status to reduce the current. During the  $t_{OFF}$  time, the commutation of the PWMx inputs are ignored.

The device returns to normal operation after a  $t_{off}$  time set according to the values of the  $R_{OFF}$  resistor and the  $C_{OFF}$  capacitor connected to TOFF pin as shown in Figure 8.

Figure 8. OFF-time regulation circuit

The recommended values for  $R_{\mbox{\scriptsize OFF}}$  and  $C_{\mbox{\scriptsize OFF}}$  are shown in Figure 9.

Short-circuiting TOFF to ground disables the current limiter.

Figure 9. t<sub>OFF</sub> vs. R<sub>OFF</sub> and C<sub>OFF</sub>

#### 5.6.1.1 Dual half-bridge and full-bridge operation mode (fixed OFF-time)

In dual half-bridge and full-bridge operation modes, the current is limited turning on both the low-side MOS (slow decay). As soon as the OFF-time expires the bridges return in the ON state (see Figure 10).

DS14341 - Rev 3 page 16/35

Figure 10. In dual half-bridge and full-bridge operation mode,

#### 5.6.1.2 Half-bridge parallel operation mode (fixed OFF-time)

In half-bridge parallel operation mode, the decay strategy is determined by the status of PWM2/PH (see Figure 11)

- PWM2/PH is low: the low-side MOS is switched on

- PWM2/PH is high: the output is in high impedance (current recirculates in the body diode)

As soon as the OFF-time expires the bridges return in the ON state (see Figure 11).

Figure 11. Current control in half-bridge parallel mode (fixed OFF-time)

#### 5.6.1.3 Mixed decay operation mode (fixed OFF-time)

In mixed decay operation mode, the current is limited turning on both the low-side MOS of the full-bridge (slow decay), the system switches from slow decay to quasi-synchronous fast decay (the sinking side of the bridge is put in high impedance) when the counter reaches a fixed threshold corresponding to a 5/8th of the total decay time ( $t_{OFF}$ ).

As soon as the OFF-time expires the bridges return in the ON state (see Figure 12).

DS14341 - Rev 3 page 17/35

Figure 12. Current control in mixed decay mode (fixed OFF-time)

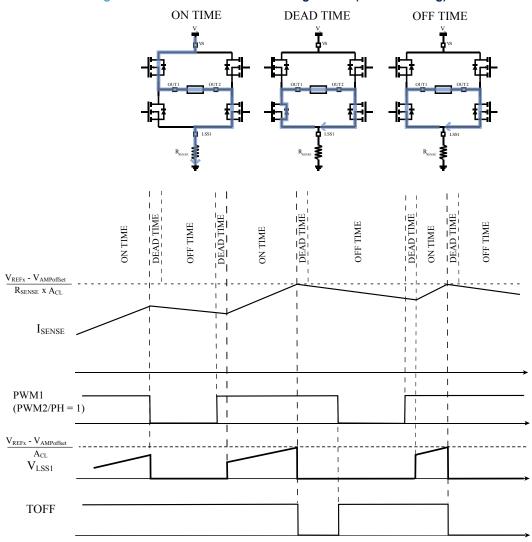

#### 5.6.2 PWM trimming mode

When  $V_1$  exceeds  $V_{REF}$  the control circuitry sets the device in limiting status to reduce the current. The decay strategy and the return to normal operation depends on the selected driving mode: full-bridge or parallel operation mode (mixed decay is not available with this current limiter mode).

In PWM trimming mode the TOFF pin is a digital output and it is forced low during the current decay time.

#### 5.6.2.1 Dual half-bridge and full-bridge operation mode (PWM trimming)

In dual half-bridge and full-bridge operation modes, the current is limited turning on both the low-side MOS (slow decay, see Figure 13. Current control in full-bridge mode (PWM trimming)). The device returns to normal operation if one of the following conditions occurs:

- nSTDBY is set low

- EN/nFAULTx is set low

- PWM1 is set low in full-bridge operation mode

- PWM1 and PWM2/PH are both set low in dual half-bridge mode

DS14341 - Rev 3 page 18/35

Figure 13. Current control in full-bridge mode (PWM trimming)

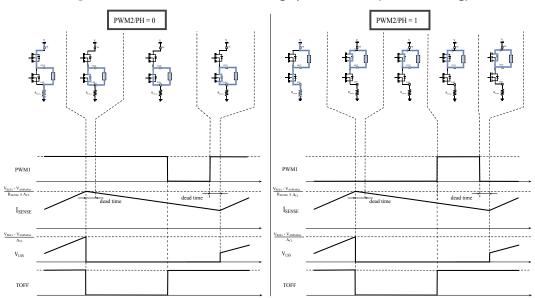

#### 5.6.2.2 Half-bridge parallel operation mode (PWM trimming)

In half-bridge parallel operation mode, the decay strategy is determined by the status of PWM2/PH (see Figure 14):

- PWM2/PH is low: the low side MOS is switched on

- PWM2/PH is high: the output is in high impedance (current recirculates in the body diode)

The device returns to normal operation if one of the following conditions occurs:

- nSTDBY is set low

- EN/nFAULTx is set low

- PWM1 is set low, if PWM2/PH = 0

- PWM1 is set high, if PWM2/PH = 1

DS14341 - Rev 3 page 19/35

Figure 14. Current control in half-bridge parallel mode (PWM trimming)

#### 5.6.3 Blanking

In order to avoid spurious triggering of the current limiter's comparator due to both internal and external noise (ringing, diode's recovery currents, etc.), the device integrates a blanking circuitry.

The blanking signal is generated at each commutation of the half-bridges 1 and 2.

When the bridge is in high impedance, blanking condition is always imposed.

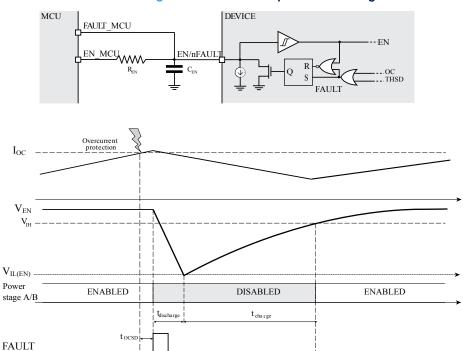

#### 5.7 Overcurrent protection

An integrated circuitry, independent from the current limiter, protects the power stage from overcurrent condition. If the current flowing into one of the integrated MOSFETs exceeds the  $I_{OC}$  threshold, the OC protection turns off all the MOSFETs and forces low the EN/nFAULT open drain output.

The device holds this condition until the nFAULT input voltage falls below the  $V_{IL}\>\>EN$  threshold.

In order to avoid spurious triggering due to noise, a deglitch filter with  $t_{\text{OCSD}}$  (OC protection) period is implemented.

DS14341 - Rev 3 page 20/35

Figure 15. Overcurrent protection timings

The total disable time after an overcurrent event can be set properly sizing the external network connected to the EN\nFAULT pin.

$t_{\rm DIS}$

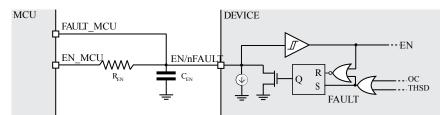

#### 5.8 Thermal shutdown

The device integrates a thermal shutdown protection. When the internal temperature exceeds the  $T_{SD}$  temperature, the power stage is disabled until the temperature returns below  $T_{SD}$  -  $T_{SD(Hyst)}$ . When the device is in thermal shutdown, the nFAULT is forced low (see Figure 16).

DS14341 - Rev 3 page 21/35

Figure 16. Thermal shutdown sequence

DS14341 - Rev 3 page 22/35

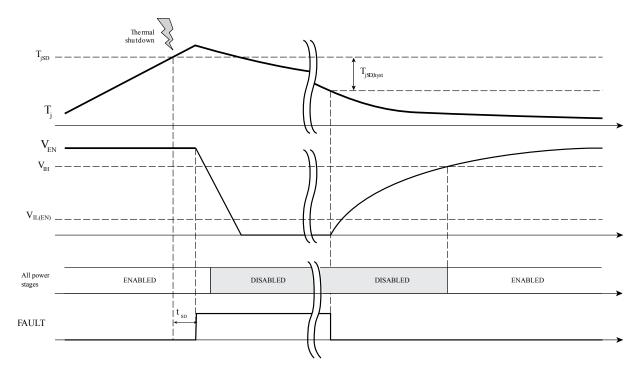

# Characterization graphs

Figure 17. Output slew rate vs. temperature ( $V_S$  = 58 V, normalized at  $T_J$  = 25 °C)

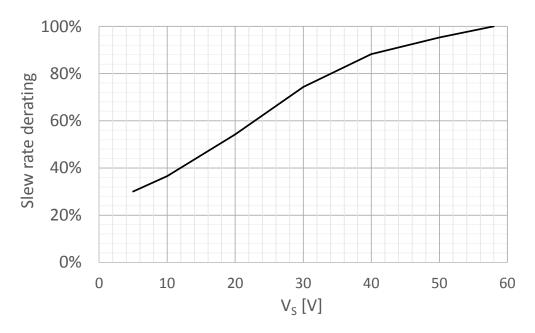

Figure 18. Output slew rate derating vs. supply voltage ( $T_J = 25$  °C)

DS14341 - Rev 3 page 23/35

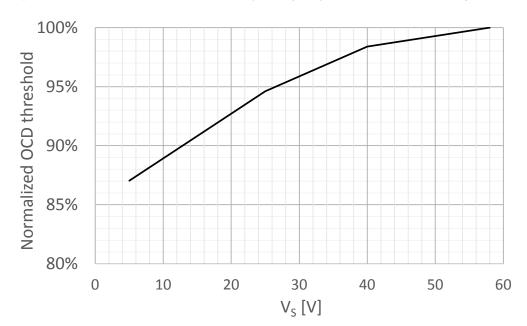

Figure 20. Overcurrent threshold vs. supply voltage ( $T_J$  = 25 °C, normalized at  $V_S$  = 58 V)

DS14341 - Rev 3 page 24/35

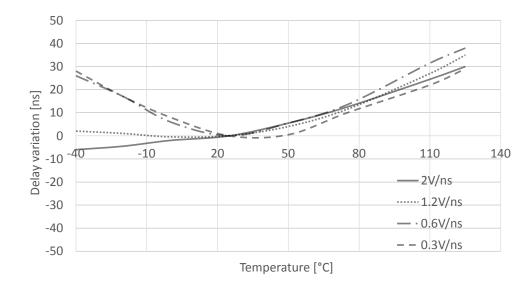

Figure 21. PWM input to output propagation delay vs. temperature (referenced to  $T_j$  = 25 °C) T

DS14341 - Rev 3 page 25/35

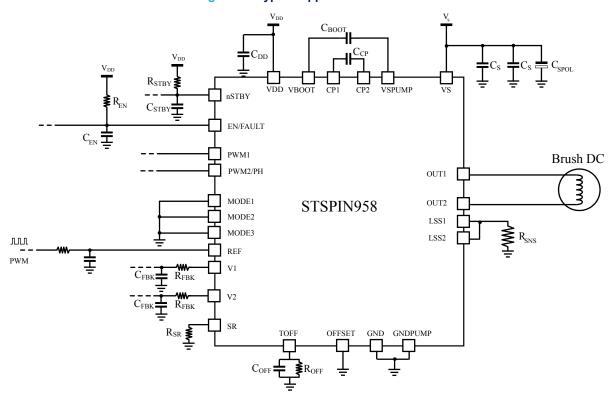

# 7 Typical application

Table 12. Typical application value

| Name                                | Value                                  |

|-------------------------------------|----------------------------------------|

| Cs                                  | 470 nF                                 |

| C <sub>BULK</sub>                   | 220 μF                                 |

| C <sub>DD</sub>                     | 220 nF                                 |

| C <sub>CP</sub>                     | 100 nF                                 |

| C <sub>BOOT</sub>                   | 1 μF                                   |

| R <sub>SNS</sub>                    | 50 mΩ / 3W                             |

| C <sub>EN</sub>                     | 10 nF                                  |

| R <sub>EN</sub>                     | 39 kΩ                                  |

| C <sub>STBY</sub>                   | 1 nF                                   |

| R <sub>STBY</sub>                   | 18 kΩ                                  |

| R <sub>OFF</sub> , C <sub>OFF</sub> | 22 kΩ, 1 nF (t <sub>OFF</sub> = 18 μs) |

| C <sub>FBK</sub>                    | 100 pF                                 |

| R <sub>FBK</sub>                    | 100 Ω                                  |

| R <sub>SR</sub>                     | 5 kΩ (SR = 0.6 V/ns)                   |

Figure 22. Typical application schematic

DS14341 - Rev 3 page 26/35

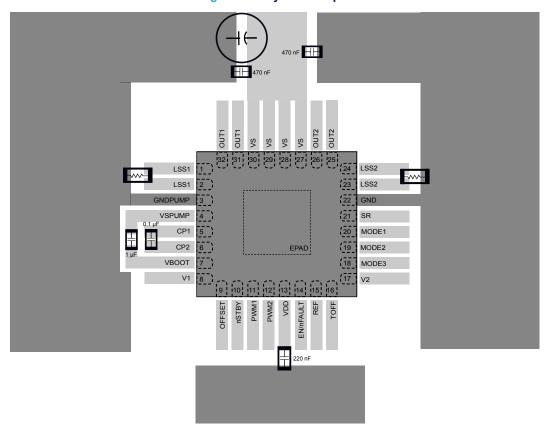

### 8 Layout guidelines

Two 470 nF bypass capacitors must be connected between the VS supply voltage pins and ground and one 220 nF bypass capacitor must be connected between the VDD supply pin and ground.

These capacitors must be low-ESR ceramic technology and placed as close to the pins as possible (VS and VDD pins) with a thick ground plane connection to the device GND pin.

A bulk capacitor is required to bypass the high current path. One or more capacitors should be placed as to minimize the length of high current paths between VS and GND. The connecting metal traces should be as wide as possible, with numerous vias connecting PCB layers.

In application requiring the device switching at high slew rates or with high output currents, ground layers should be designed to separate digital and power ground. In this case, the exposed PAD must be connected to the power ground and the VDD bypass capacitor to the digital ground. The path between the ground of the shunt resistors and the ceramic bypass capacitor of the device is critical; for this reason it must be as short as possible minimizing parasitic inductances that can cause voltage spikes on the SENSE and OUT pins.

The current sense resistors should be placed as close as possible to the device pins to minimize trace inductance between the device pin and resistors avoiding, where possible, to place them on a different board layer.

A low-ESR ceramic capacitor must be placed between the CP1 and CP2 pins (100 nF, rated for 16V) and between the VBOOT and VSPUMP pins (1  $\mu$ F, rated for 16 V).

A layout example is shown in Figure 23. Layout example.

Figure 23. Layout example

DS14341 - Rev 3 page 27/35

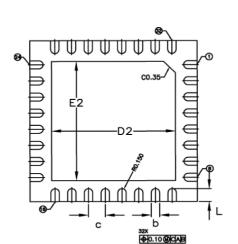

# 9 Package information

In order to meet environmental requirements, STMicroelectronics offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions, and product status are available at <a href="https://www.st.com">www.st.com</a>. ECOPACK is an STMicroelectronics trademark. A customized VFQFPN32 5 x 5 package is proposed. A smaller EPAD, internally connected to the ground pin, is desired to place through holes on the bottom of the package. Lead plating is Nickel/Palladium/Gold (Ni/Pd/Au).

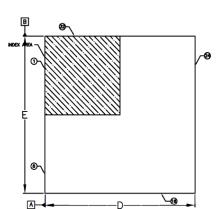

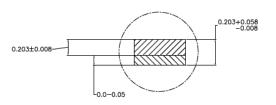

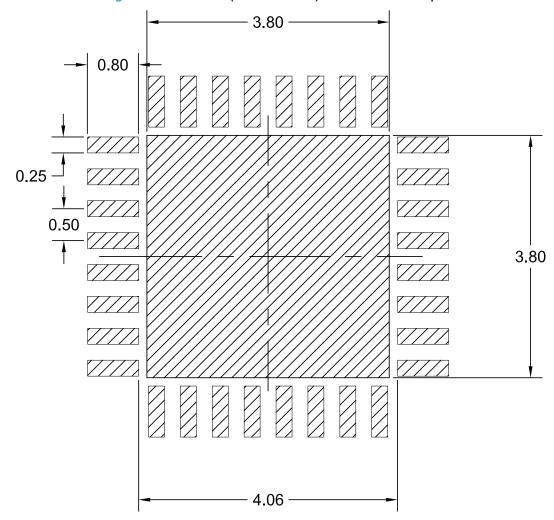

#### 9.1 VFQFPN32 5 x 5 package information

Figure 24. VFQFPN32 (5 x 5 x 1.0 mm) package outline

**BOTTOM VIEW**

**TOP VIEW**

SIDE VIEW

### **DETAIL A**

DS14341 - Rev 3 page 28/35

Table 13. VFQFPN32 (5 x 5 x 1.0 mm) package mechanical data

| Dim.   | (mm) |      |      |  |

|--------|------|------|------|--|

| Dilli. | Min. | Тур. | Max. |  |

| Α      | 0.90 | 0.95 | 1.00 |  |

| A1     | 0    |      | 0.05 |  |

| A3     |      | 0.20 |      |  |

| b      | 0.20 | 0.25 | 0.30 |  |

| D      | 4.90 | 5.00 | 5.10 |  |

| D2     | 3.60 | 3.70 | 3.80 |  |

| С      | 0.50 |      |      |  |

| E      | 4.90 | 5.00 | 5.10 |  |

| E2     | 3.60 | 3.70 | 3.80 |  |

| L      | 0.30 | 0.40 | 0.50 |  |

Figure 25. VFQFPN32 (5 x 5 x 1.0 mm) recommended footprint

DS14341 - Rev 3 page 29/35

# 10 Ordering information

Table 14. Device summary

| Order code  | Package                   | Packaging     |

|-------------|---------------------------|---------------|

| STSPIN958TR | VFQFPN32 5 x 5 x 1 – 32 L | Tape and reel |

| STSPIN958   | VFQFPN32 5 x 5 x 1 – 32 L | Tray          |

DS14341 - Rev 3 page 30/35

# **Revision history**

Table 15. Document revision history

| Date        | Version | Changes                                        |

|-------------|---------|------------------------------------------------|

| 07-Jul-2023 | 1       | Initial release.                               |

| 25-Oct-2023 | 2       | Added P/N in Table 14                          |

| 29-Oct-2024 | 3       | Updated description and figures in Section 5.6 |

DS14341 - Rev 3 page 31/35

# **Contents**

| 1    | Bloc   | k diagr  | am                                              | 2  |

|------|--------|----------|-------------------------------------------------|----|

| 2    | Elec   | trical d | ata                                             | 3  |

|      | 2.1    | Absolu   | ute maximum ratings                             | 3  |

|      | 2.2    | Recon    | nmended operating conditions                    | 3  |

|      | 2.3    | ESD p    | protection ratings                              | 4  |

|      | 2.4    | Therm    | nal data                                        | 5  |

| 3    | Elec   | trical c | haracteristics                                  | 6  |

| 4    | Pin    | descrip  | tion                                            | 8  |

| 5    |        |          | 1                                               |    |

|      | 5.1    | Power    | supply                                          | 10 |

|      | 5.2    | Power    | stages and charge pump circuitry                | 11 |

|      | 5.3    |          | ated operational amplifiers                     |    |

|      | 5.4    | Driving  | g logic                                         | 11 |

|      |        | 5.4.1    | Dual half-bridge mode                           | 12 |

|      |        | 5.4.2    | Single full-bridge mode                         | 13 |

|      |        | 5.4.3    | Single half-bridge mode - parallel operation    | 14 |

|      |        | 5.4.4    | Single full-bridge mode – mixed decay operation | 15 |

|      | 5.5    | Stand    | by                                              | 15 |

|      | 5.6    | PWM      | current control                                 | 15 |

|      |        | 5.6.1    | Fixed OFF-time mode                             | 16 |

|      |        | 5.6.2    | PWM trimming mode                               | 18 |

|      |        | 5.6.3    | Blanking                                        |    |

|      | 5.7    |          | urrent protection                               |    |

|      | 5.8    |          | nal shutdown                                    |    |

| 6    | Cha    | racteriz | ation graphs                                    | 23 |

| 7    | Typi   | cal app  | lication                                        | 26 |

| 8    | Lay    | out guid | delines                                         | 27 |

| 9    | Pacl   | kage in  | formation                                       | 28 |

|      | 9.1    | VFQF     | PN32 5 x 5 package information                  | 28 |

| 10   | Orde   | ering in | formation                                       | 30 |

| Rev  | ision  | history  | ·                                               | 31 |

| List | of tal | bles     |                                                 | 33 |

| List | of fig | jures    |                                                 | 34 |

|      |        |          |                                                 |    |

# **List of tables**

| Table 1.  | Absolute maximum ratings                                   | . 3 |

|-----------|------------------------------------------------------------|-----|

| Table 2.  | Recommended operating conditions                           | . 3 |

| Table 3.  | ESD protection ratings                                     | . 4 |

| Table 4.  | Thermal data                                               |     |

| Table 5.  | Electrical characteristics                                 | . 6 |

| Table 6.  | Pad list                                                   | . 8 |

| Table 7.  | Slew rate selection                                        | 11  |

| Table 8.  | Driving mode selection                                     | 12  |

| Table 9.  | Truth table – dual half-bridge mode                        | 12  |

| Table 10. | Truth table – single full-bridge mode                      | 13  |

| Table 11. | Truth table – single half-bridge mode (parallel operation) | 14  |

| Table 12. | Typical application value                                  | 26  |

| Table 13. | VFQFPN32 (5 x 5 x 1.0 mm) package mechanical data          | 29  |

| Table 14. | Device summary                                             | 30  |

| Table 15. | Document revision history                                  | 31  |

# **List of figures**

| Figure 1.  | Block diagram                                                                                          | . 2 |

|------------|--------------------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Pin connection                                                                                         | . 8 |

| Figure 3.  | Power-up and power-down sequences                                                                      | 10  |

| Figure 4.  | Charge pump circuitry                                                                                  | 11  |

| Figure 5.  | Driver time diagram - dual half-bridge mode                                                            | 13  |

| Figure 6.  | Driver time diagram - single full-bridge mode                                                          | 14  |

| Figure 7.  | Driver time diagram - single half-bridge mode (parallel operation)                                     | 15  |

| Figure 8.  | OFF-time regulation circuit                                                                            | 16  |

| Figure 9.  | $t_{OFF}$ vs. $R_{OFF}$ and $C_{OFF}$                                                                  | 16  |

| Figure 10. | In dual half-bridge and full-bridge operation mode,                                                    | 17  |

| Figure 11. | Current control in half-bridge parallel mode (fixed OFF-time)                                          | 17  |

| Figure 12. | Current control in mixed decay mode (fixed OFF-time)                                                   | 18  |

| Figure 13. | Current control in full-bridge mode (PWM trimming)                                                     | 19  |

| Figure 14. | Current control in half-bridge parallel mode (PWM trimming)                                            | 20  |

| Figure 15. | Overcurrent protection timings                                                                         | 21  |

| Figure 16. | Thermal shutdown sequence                                                                              |     |

| Figure 17. | Output slew rate vs. temperature ( $V_S$ = 58 V, normalized at $T_J$ = 25 °C)                          | 23  |

| Figure 18. | Output slew rate derating vs. supply voltage (T <sub>J</sub> = 25 °C)                                  | 23  |

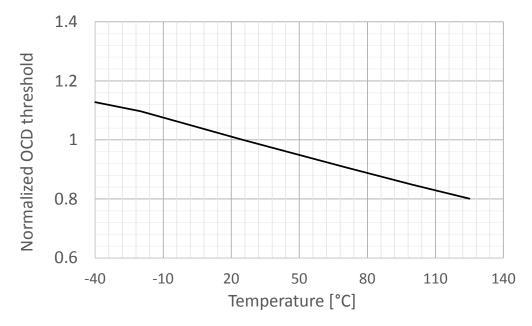

| Figure 19. | Overcurrent threshold vs. temperature (V <sub>S</sub> = 58 V, normalized at T <sub>J</sub> = 25 °C)    | 24  |

| Figure 20. | Overcurrent threshold vs. supply voltage (T <sub>J</sub> = 25 °C, normalized at V <sub>S</sub> = 58 V) | 24  |

| Figure 21. | PWM input to output propagation delay vs. temperature (referenced to T <sub>j</sub> = 25 °C) T         | 25  |

| Figure 22. | Typical application schematic                                                                          | 26  |

| Figure 23. | Layout example                                                                                         | 27  |

| Figure 24. | VFQFPN32 (5 x 5 x 1.0 mm) package outline                                                              | 28  |

| Figure 25. | VFQFPN32 (5 x 5 x 1.0 mm) recommended footprint.                                                       | 29  |

DS14341 - Rev 3 page 34/35

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 STMicroelectronics – All rights reserved

DS14341 - Rev 3 page 35/35